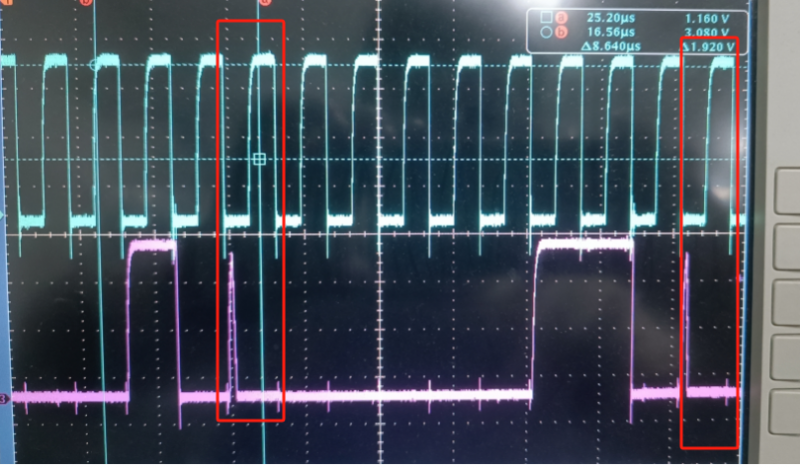

在I2C的波形中,經(jīng)常會發(fā)現(xiàn)有這樣的脈沖毛刺,會被認(rèn)為是干擾或者器件不正常。

看到這個波形時,可以先數(shù)一下出現(xiàn)在第幾個clock的位置,如果出現(xiàn)在第9個clock的低電平期間,就不是干擾或者器件異常導(dǎo)致。

在I2C的協(xié)議中,不管是地址匹配階段還是數(shù)據(jù)讀寫階段,第9個clock都是ACK和NACK位;

其中NACK為第9個SCL上升沿時SDA高電平:

ACK為第9個SCL上升沿時SDA低電平:

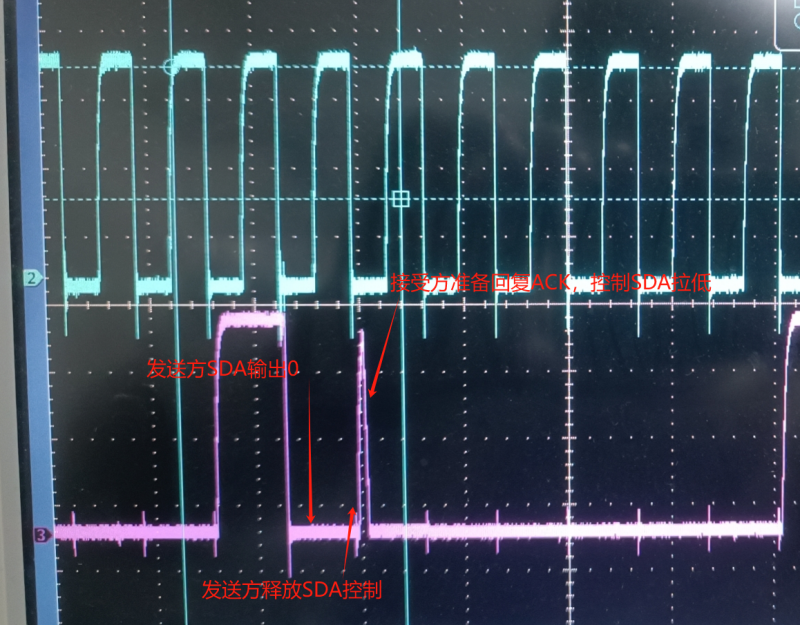

在地址匹配階段由從機來回復(fù)ACK,在數(shù)據(jù)收發(fā)階段由接受方來回復(fù)ACK。

那么I2C是雙向半雙工通信,SDA引腳通過主機和從機共同控制,ACK回復(fù)過程意味著發(fā)送方會在通過SDA發(fā)送了8個bit的數(shù)據(jù)后釋放SDA控制權(quán)給接受方,此時如果最后一個波形數(shù)據(jù)BIT0是0,那SDA會在SCL下降沿后從拉低狀態(tài)被釋放,由于上拉電阻的作用SDA就會恢復(fù)到高電平,但緊接著接受方開始數(shù)據(jù)建立開啟對SDA的控制權(quán),拉低SDA引腳準(zhǔn)備回復(fù)ACK,于是SDA信號被再次拉低。

由于整個過程是連續(xù)的,且都會在SCL第9個Clock的低電平期間完成,產(chǎn)生的波形就會像一個毛刺被誤認(rèn)為干擾。實際上這個波形的出現(xiàn)不用在意,可以不采取任何措施。